网站首页生活常识 >正文

推进半导体芯片技术的核心是一个严峻的挑战:创造更小、更高效的电子元件。这一挑战在光刻领域尤其明显,光刻是一种在半导体材料(称为晶圆)上创建复杂图案以生产芯片的工艺。

光刻使用一种称为光掩模(或简称掩模)的模板来在半导体晶圆上创建图案。该行业一直在寻找提高掩模和晶圆的分辨率和可制造性的方法,这将生产出更快的芯片,并具有更高的正常运行芯片产量。

提高分辨率和图案保真度的计算光刻技术,例如光学邻近校正(OPC),通过修改单个掩模图案以改善掩模和晶圆印刷,在应对这些挑战方面取得了重大进展。

逆向光刻技术(ILT)是一种数学上严格的逆向方法,可确定将产生所需的晶圆结果的掩模形状,已被视为解决先进芯片光刻的许多挑战的有前途的解决方案。自十多年前推出以来,已有大量研究表明,曲线ILT掩模形状尤其能产生最佳晶圆效果。

然而,直到最近,与这种计算技术相关的运行时间还限制了其在芯片上关键“热点”的实际应用。2019年,提出了一种全新的专用系统,其中包括一种独特的GPU加速方法,该方法模拟单个巨型GPU/CPU对,可以同时计算整个全芯片ILT解决方案。这种新颖的方法是为ILT和GPU加速而系统设计的,使全芯片ILT在生产中成为现实。

然而,这种方法依赖于多光束掩模写入,这是掩模写入的一个重要的新发展,它是基于像素的,因此在写入时间方面与形状无关。剩下的问题是,全芯片曲线ILT的优势是否可以扩展到可变形状光束(VSB)掩模写入器,这些掩模写入器写入直线(有时是三角形)形状而不是像素,并且构成掩模写入器的大部分今天世界各地。

虽然VSB写入器通过一次写入一个矩形镜头来快速创建较大的矩形形状,但复杂的掩模图案可能是一个问题,因为创建它们所需的大量小矩形会花费很长时间来写入。

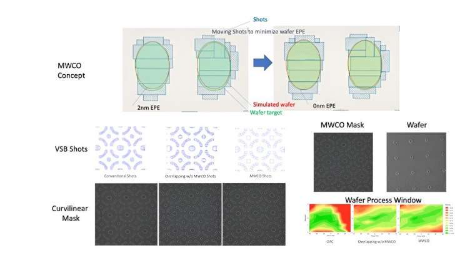

D2S,Inc.的团队在《微/纳米图案、材料和计量杂志》上报告了他们的工作,发明了一种称为掩模晶圆协同优化(MWCO)的方法,该方法具有三个见解:掩模写入器和晶圆扫描仪都是低功耗的。通过过滤器;由掩模/晶圆模拟引导的重叠镜头可以用更少的镜头创建曲线形状;通过瞄准晶圆图案而不是掩模图案,人们可以创建更简单的镜头来打印正确的晶圆图案。通过使用这种双重模拟,晶圆印刷质量得到迭代优化,同时操纵VSB发射边缘以产生已知可在VSB写入器上写入的直线目标掩模形状,并具有已知且可接受的发射数量。

D2S和美光科技已经证明,与美光OPC相比,MWCO可以将晶圆变异减少3倍,并且可以将晶圆工艺窗口提高2倍,这表明光刻工艺的精度和可靠性得到了大幅提高。全曲线ILT掩模的写入时间将小于12小时,满足大批量生产要求。

这意味着所有半导体制造商现在都可以生产出不仅尺寸

版权说明:本站所有作品图文均由用户自行上传分享,仅供网友学习交流。若您的权利被侵害,请联系我们

相关文章:

- 2024-02-21研究人员对配位键断裂制备MOF基阻燃剂进行全面综述

- 2024-02-20研究人员开发出受珊瑚触手启发的防污膜垫片

- 2024-02-20研究人员解开了巨型南极海蜘蛛的繁殖之谜

- 2024-02-20为什么在俄亥俄州发现的两种史前鲨鱼有新名字

- 2024-02-20变色龙激发了新的多色3D打印技术

- 2024-02-20量子暗态在降噪方面具有优势

- 2024-02-19饲喂植物补充剂的日粮的奶牛可以更有效地利用能量

- 2024-02-19研究警告说误导性的重新造林计划威胁着非洲大片热带草原

- 2024-02-19研究人员推出了新模型在个体尺度和生态系统层面上架起生命规则的桥梁

- 站长推荐

- 栏目推荐